b_asic.architecture¶

B-ASIC architecture classes.

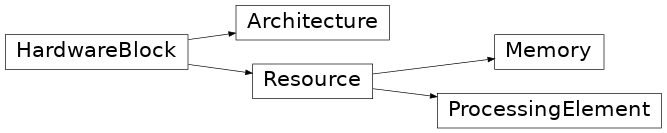

- class b_asic.architecture.Architecture(processing_elements: ProcessingElement | Iterable[ProcessingElement], memories: Memory | Iterable[Memory], entity_name: str = 'arch', direct_interconnects: ProcessCollection | None = None)¶

Class representing an architecture.

- Parameters:

- processing_elements

ProcessingElementor iterable ofProcessingElement The processing elements in the architecture.

- memories

Memoryor iterable ofMemory The memories in the architecture.

- entity_namestr, default: “arch”

Name for the top-level entity.

- direct_interconnects

ProcessCollection, optional Process collection of zero-time memory variables used for direct interconnects.

- processing_elements

- assign_resources(heuristic: str = 'left_edge') None¶

Convenience method to assign all resources in the architecture.

- Parameters:

- heuristicstr, default: “left_edge”

The heurstic to use.

See also

- property direct_interconnects: ProcessCollection | None¶

- get_interconnects_for_memory(mem: Memory | str) Tuple[Dict[Resource, int], Dict[Resource, int]]¶

Return a dictionary with interconnect information for a Memory.

- Parameters:

- mem

Memoryor str The memory or entity name to obtain information about.

- mem

- Returns:

- (dict, dict)

A dictionary with the ProcessingElements that are connected to the write and read ports, respectively, with counts of the number of accesses.

- get_interconnects_for_pe(pe: str | ProcessingElement) Tuple[List[Dict[Tuple[Resource, int], int]], List[Dict[Tuple[Resource, int], int]]]¶

Return with interconnect information for a ProcessingElement.

The information is tuple, where each element is a lists of dictionaries.

- Parameters:

- pe

ProcessingElementor str The processing element or entity name to get information for.

- pe

- Returns:

- list

List of dictionaries indicating the sources for each import and the frequency of accesses.

- list

List of dictionaries indicating the sources for each outport and the frequency of accesses.

- move_process(proc: str | Process, source: str | Resource, destination: str | Resource, assign: bool = False) None¶

Move a

Processfrom oneResourceto another.Both the resource moved from and will become unassigned after a process has been moved, unless assign is True.

- Parameters:

- proc

Processor str The process (or its name) to move.

- source

Resourceor str The resource (or its entity name) to move the process from.

- destination

Resourceor str The resource (or its entity name) to move the process to.

- assignbool, default=False

Whether to perform assignment of the resources after moving.

- proc

- Raises:

KeyErrorIf proc is not present in resource source.

- property processing_elements: List[ProcessingElement]¶

- remove_resource(resource: str | Resource) None¶

Remove an empty

Resourcefrom the architecture.- Parameters:

- resource

Resourceor str The resource or the resource name to remove.

- resource

- resource_from_name(name: str) Resource¶

Get

Resourcebased on name.- Parameters:

- namestr

Name of the resource.

- Returns:

- set_entity_name(entity_name: str) None¶

Set entity name of hardware block.

- Parameters:

- entity_namestr

The entity name.

- write_code(path: str) None¶

Write VHDL code for hardware block.

- Parameters:

- pathstr

Directory to write code in.

- class b_asic.architecture.HardwareBlock(entity_name: str | None = None)¶

Base class for architectures and resources.

- Parameters:

- entity_namestr, optional

The name of the resulting entity.

- set_entity_name(entity_name: str) None¶

Set entity name of hardware block.

- Parameters:

- entity_namestr

The entity name.

- write_code(path: str) None¶

Write VHDL code for hardware block.

- Parameters:

- pathstr

Directory to write code in.

- class b_asic.architecture.Memory(process_collection: ProcessCollection, memory_type: Literal['RAM', 'register'] = 'RAM', entity_name: str | None = None, read_ports: int | None = None, write_ports: int | None = None, total_ports: int | None = None, assign: bool = False)¶

Create a memory from a ProcessCollection with memory variables.

- Parameters:

- process_collection

ProcessCollection The ProcessCollection to create a Memory for.

- memory_type{‘RAM’, ‘register’}

The type of memory.

- entity_namestr, optional

Name of memory entity.

- read_portsint, optional

Number of read ports for memory.

- write_portsint, optional

Number of write ports for memory.

- total_portsint, optional

Total number of read and write ports for memory.

- assignbool, default False

Perform assignment when creating the Memory (using the default properties).

- process_collection

- assign(heuristic: str = 'left_edge') None¶

Perform assignment of the memory variables.

- Parameters:

- heuristicstr, default: ‘left_edge’

The assignment algorithm. Depending on memory type the following are available:

- ‘RAM’

‘left_edge’: Left-edge algorithm.

‘graph_color’: Graph-coloring based on exclusion graph.

- ‘register’

…

- property collection: ProcessCollection¶

- property content: Figure¶

Return a graphical representation of the content.

This is visible in enriched shells, but the object itself has no further meaning (it is a Matplotlib Figure).

- property operation_type: Type[MemoryProcess]¶

- plot_content(ax: Axes, **kwargs) None¶

Plot the content of the resource.

This plots the assigned processes executed on this resource.

- Parameters:

- axAxes

Matplotlib Axes to plot in.

- **kwargs

Passed to

plot().

- remove_process(proc: Process, assign: bool = False)¶

Remove a

Processfrom thisResource.Raises

KeyErrorif the process being added is not of the same type as the other processes.

- set_entity_name(entity_name: str) None¶

Set entity name of hardware block.

- Parameters:

- entity_namestr

The entity name.

- show_content(title=None, **kwargs) None¶

Display the content of the resource.

This displays the assigned processes executed on this resource.

- Parameters:

- titlestr, optional

Figure title.

- **kwargs

Passed to

plot().

- write_code(path: str) None¶

Write VHDL code for hardware block.

- Parameters:

- pathstr

Directory to write code in.

- class b_asic.architecture.ProcessingElement(process_collection: ProcessCollection, entity_name: str | None = None, assign: bool = True)¶

Create a processing element for a ProcessCollection with OperatorProcesses.

- Parameters:

- process_collection

ProcessCollection Process collection containing operations to map to processing element.

- entity_namestr, optional

Name of processing element entity.

- assignbool, default True

Perform assignment when creating the ProcessingElement.

- process_collection

- assign(heuristic: Literal['left_edge', 'graph_color'] = 'left_edge') None¶

Perform assignment of the processes.

- Parameters:

- heuristic{‘left_edge’, ‘graph_color’}, default: ‘left_edge’

The assignment algorithm.

‘left_edge’: Left-edge algorithm.

‘graph_color’: Graph-coloring based on exclusion graph.

- property collection: ProcessCollection¶

- property content: Figure¶

Return a graphical representation of the content.

This is visible in enriched shells, but the object itself has no further meaning (it is a Matplotlib Figure).

- plot_content(ax: Axes, **kwargs) None¶

Plot the content of the resource.

This plots the assigned processes executed on this resource.

- Parameters:

- axAxes

Matplotlib Axes to plot in.

- **kwargs

Passed to

plot().

- property processes: List[OperatorProcess]¶

- remove_process(proc: Process, assign: bool = False)¶

Remove a

Processfrom thisResource.Raises

KeyErrorif the process being added is not of the same type as the other processes.

- set_entity_name(entity_name: str) None¶

Set entity name of hardware block.

- Parameters:

- entity_namestr

The entity name.

- show_content(title=None, **kwargs) None¶

Display the content of the resource.

This displays the assigned processes executed on this resource.

- Parameters:

- titlestr, optional

Figure title.

- **kwargs

Passed to

plot().

- write_code(path: str) None¶

Write VHDL code for hardware block.

- Parameters:

- pathstr

Directory to write code in.

- class b_asic.architecture.Resource(process_collection: ProcessCollection, entity_name: str | None = None)¶

Base class for resource.

- Parameters:

- process_collection

ProcessCollection The process collection containing processes to be mapped to resource.

- entity_namestr, optional

The name of the resulting entity.

- process_collection

- assign(heuristic: str = 'left_edge')¶

Perform assignment of processes to resource.

- Parameters:

- heuristicstr

See the specific resource types for more information.

See also

- property collection: ProcessCollection¶

- property content: Figure¶

Return a graphical representation of the content.

This is visible in enriched shells, but the object itself has no further meaning (it is a Matplotlib Figure).

- property operation_type: Type[MemoryProcess] | Type[Operation]¶

- plot_content(ax: Axes, **kwargs) None¶

Plot the content of the resource.

This plots the assigned processes executed on this resource.

- Parameters:

- axAxes

Matplotlib Axes to plot in.

- **kwargs

Passed to

plot().

- remove_process(proc: Process, assign: bool = False)¶

Remove a

Processfrom thisResource.Raises

KeyErrorif the process being added is not of the same type as the other processes.

- set_entity_name(entity_name: str) None¶

Set entity name of hardware block.

- Parameters:

- entity_namestr

The entity name.

- show_content(title=None, **kwargs) None¶

Display the content of the resource.

This displays the assigned processes executed on this resource.

- Parameters:

- titlestr, optional

Figure title.

- **kwargs

Passed to

plot().

- write_code(path: str) None¶

Write VHDL code for hardware block.

- Parameters:

- pathstr

Directory to write code in.